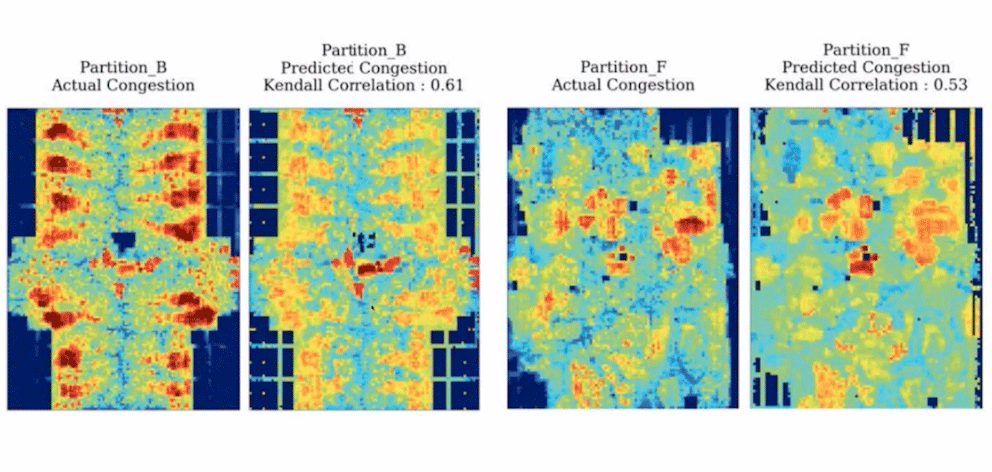

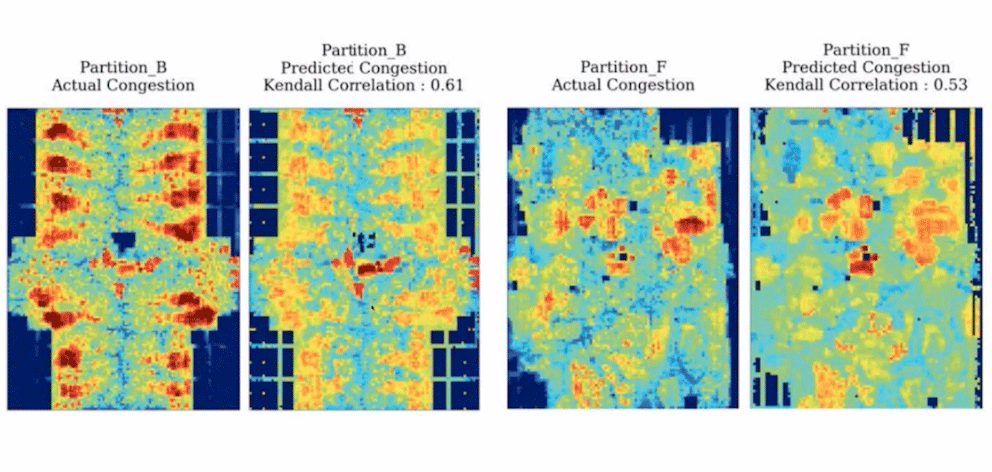

Перегруженность интегральной схемы, где через отдельные участки проходит слишком много цепей (красным цветом)

Сегодня в РФ рассматриваются планы создать полноценную инфраструктуру для производства микросхем, организовать 300 дизайн-центров с штатом минимум по 100 профильных специалистов и запустить новые фабрики. В этой связи интересно посмотреть, какие методы ML используются в проектировании современной микроэлектроники. Что-то можно перенять для отечественных разработок.

AI и ML — новый уровень проектирования ИС

Модели машинного обучения (ML) по своей сути оптимально подходят для проектирования ИС, потому что современные микросхемы с миллиардами транзисторов — это сложнейшие системы, параметры работы которых становится трудно рассчитать конвенциальными способами.

Более того, само производство ИС носит статистический характер, что тоже должны учитывать проектировщики.

Очевидно, что ИИ можно внедрить на разных уровнях проектирования. Например, для калибровки, см. статью «Использование машинного обучения для калибровки аналоговых микросхем» («Вестник Воронежского государственного технического университета»).

Другой очевидный способ: взять существующие инструменты САПР — и подключить к ним модули ML для оптимизации отдельных расчётов. Здесь нейросети значительно ускоряют вычисления, в некоторых случаях на несколько порядков.

В последнее время на рынке появляется всё больше специализированных инструментов AI/ML для САПР, таких как Synopsys или Cadence Cerebrus Intelligent Chip Explorer от компании Cadence Design Systems и другие. В рекламных слайдах разработчики из Cadence заявляют, что с помощью таких интеллектуальных инструментов проектирования один инженер способен быстро выполнять работу, которая раньше требовала многих месяцев ручного труда от группы проектировщиков.

Конечно, выглядит как маркетинг. Но что говорят реальные инженеры, которые непосредственно своими руками выполняют проектирование микросхем с помощью подобных инструментов?

Ведущий исследователь научно-исследовательского подразделения компании Nvidia Билл Дэлли в своём выступлении на конференции GTC 2022 привёл несколько интересных примеров, как Nvidia использует ML в разработке и оптимизации микросхем. Это самая актуальная информация непосредственно о текущих разработках дизайн-центра Nvidia R&D, в котором сейчас работает около 300 инженеров. Все технические процессы описаны в четырёх научных статьях, указанных под иллюстрациями (1, 2, 3, 4, плюс статья по NVCell).

Составление карты падения напряжения

Например, один из инструментов ИИ в системе САПР берёт схему электрической цепи в микросхеме GPU — и оценивает, как в различных ситуациях упадёт напряжение (IR Drop Estimation). Такой расчёт в обычной коммерческой САПР занимает три часа, а модель выполняет его за 18 минут (выделение признаков) плюс 3 секунды (непосредственно расчёт), сказал Дэлли.

Как показано на иллюстрации, после соответствующего обучения модель ML эффективно усваивает коэффициенты и показывает точность 94% (в трёхсекундном выводе).

В данном случае используется не свёрточная, а графовая нейросеть (GNN). Она оценивает частоту переключения различных узлов в цепи, что позволяет вывести итоговую оценку напряжения.

Прогнозирование паразитных характеристик

Билл Дэлли говорит, что это его любимая сфера использования ML, потому что он и сам много времени провёл за расчётом паразитных характеристик с помощью графовых нейросетей. В прежние времена проектирование схем было итеративным процессом. Разработчик топологии рисовал схему и каждый транзистор на ней, как на нижней иллюстрации слева.

Но вы не знали, как она будет реально работать, пока специалист по проведению физической верификации проекта (layout designer) не возьмёт эту схему, не сделает макет и не посчитает паразитные характеристики. Только после этого вы могли запустить моделирование схемы и обнаружить, что она не соответствует некоторым спецификациям. Приходилось возвращаться, изменять схему — и снова отправлять её на физическую верификацию макета. Очень долгий, итеративный и крайне трудоёмкий процесс.

Теперь можно обучить нейросети предсказывать паразитные характеристики без необходимости делать макет. Как показано на графике вверху, модель выдаёт довольно точный расчёт.

Заторы маршрутизации

Кроме того, модели ML используются для расчёта перегруженности маршрутов — и поиска потенциальных заторов в маршрутизации на ИС. Это очень важно при компоновке микросхем.

В обычном случае нужно взять список сетей и прогнать процесс размещения и маршрутизации, что требует много времени, зачастую даже несколько дней. И только потом мы получаем фактическую картину по перегруженности и заторам. И понимаем, что первоначальные схемы не годятся. Нужно их рефакторить, прокладывая схемы в обход красных областей (на иллюстрации), через которые проходит слишком много цепей.

Модель на основе графовых сетей берёт список сетей и предсказывает области заторов. Она работает не абсолютно идеально, но примерно показывает, где могут быть проблемы, чего во многих случаях вполне достаточно для ускорения итераций. Таким образом, итерации проектирования микросхемы сокращаются с нескольких дней до нескольких минут.

Апгрейд микросхем на новый техпроцесс

Все перечисленные выше подходы работают по схожему принципу: они исправляют ошибки в дизайне, который выполнил человек. Но гораздо интереснее посмотреть на примеры работы, где ИИ составляет собственные проекты.

Билл Дэлли привёл два таких примера. Первый из них — фирменная система под названием NVCell (имитация отжига + обучение с подкреплением) для разработки «стандартной библиотеки» ячеек. Каждый раз, когда Nvidia переходит на новый техпроцесс, например, с 7 нм на 5 нм, она использует эту библиотеку. Что такое ячейка? Это базовый элемент цифровой схемы вроде логических вентилей AND и OR или полного сумматора. Библиотека содержит много тысяч таких ячеек, которые следует перепроектировать под новую технологию производства с очень сложным набором правил проектирования.

«В основном, для размещения транзисторов мы используем обучение с подкреплением, — говорит Дэлли. — Но после их размещения обычно возникает куча ошибок в правилах проектирования, это происходит почти как в игре Atari [скорее всего, Дэлли имеет в виду известные примеры, как нейросеть DeepMind самостоятельно обучалась побеждать в старых играх Atari методом проб и ошибок — прим. пер.]. Это похоже на Atari, только наша видеоигра — это исправление правил проектирования в стандартной ячейке. Проходя и исправляя эти ошибки правил проектирования с помощью обучения с подкреплением, мы можем в основном завершить проектирование наших стандартных ячеек».

На последнем слайде показано, что 92% библиотеки ячеек составлено с помощью этого инструмента без ошибок. В 12% случаев ячейки меньше по размеру, чем спроектированные человеком. В целом по уровню сложности NVCell работает не хуже человека.

По словам ведущего исследователя Nvidia R&D, составление такой библиотеки вручную требовало почти года работы группы из десяти человек, а сейчас — всего несколько дней работы двух графических процессоров. Причём во многих случаях дизайн лучше, чем у человека.

Конечно, люди не останутся без работы. Они могут уделить внимание не рутинному труду, а более сложным и интересным задачам, Например, тем 8% ячеек, которые NVCell не сумела спроектировать автоматически.

Второй пример обучения с подкреплением — система PrefixRL для проектирования параллельных префиксных схем, где реально создаётся роль агента (дизайн), действующего во враждебном окружении (физическая схема), чтобы победить, а в качестве стимулов для победы заложены минимизация площади микросхемы и задержки передачи сигнала.

Видеозапись доклада Дэлли (42 мин 40 сек) опубликована на сайте конференции GCC 2022 и доступна после бесплатной регистрации в Nvidia Developer Program.

Документ PDF со слайдами презентации см. здесь.

Автор презентации Билл Дэлли в своей домашней лаборатории

P. S. Теоретически, если бы ИИ мог самостоятельно проектировать микросхемы и оптимизировать их, это означало бы прямую дорогу к сингулярности. Однако мы пока далеки от такого. На самом деле разработка каждой модели ML требует труда квалифицированных специалистов, без этого никак не обойтись.